-

大部分计算机仍属于冯·诺依曼机

-

浮点数中数符决定数的正负

-

原码:有

+0-0之分、有两种形式

补码只有一种形式 -

内存:用于存放当前正在使用的程序和数据

-

多级存储体系目的:解决存储容量、访问速度和价格之间的矛盾

-

cache是一种高速缓冲存储器

-

cache原理

当 CPU 读取内存中一个字时,便发出此字的内存地址到cache 和主存。此时 cache 控制逻辑依据地址判断此字当前是否在 cache 中:若是,则 cache 命中,此字立即传送给 CPU;若非,则 cache 缺失,用主存读周期把此字从主存读出送到 CPU,与此同时,把含有这个字的整个数据块从主存读出送到cache 中。 -

cache替换策略

- 最不经常使用(LFU)算法

- 近期最少使用(LRU)算法

- 随机替换

-

虚拟存储器分为

- 页式虚拟存储器

- 段式虚拟存储器

- 段页式虚拟存储器

-

当操作数不在内存中,而是在CPU的通用寄存器中时,可采用

寄存器寻址方式。

寄存器间接寻址方式操作数在内存中。 -

一个较为完善的指令系统,应当有

数据处理数据存储数据传送程序控制。 -

运算器中算术逻辑运算单元(ALU)包括

算术运算逻辑运算。 -

指令寄存器用来保存当前正在执行的一条指令。

-

后继地址寄存器也叫程序计数器。

-

计算机之所以能自动地工作,是因为CPU能从存放程序对的内存中

取出一条指令并执行这条指令。 -

CPU周期又称为

机器周期。

一个CPU周期时间又包含有若干个时钟周期。 -

LAD指令的取值周期

- 和MOV一样

-

LAD指令的执行周期

- 1)操作控制器 OC发出控制命令打开 IR 输出三态门,将指令中的直接地址码6放到线DBUS 上;

- 2)OC发出操作命令,将地址码6装入数存地址寄存器 AR;

- 3)OC发出读命令,将数存6号单元中的数100读出到 DBUS 上;

- 4)OC发出命令,将DBUS上的数据100装入缓冲寄存器 DR;

- 5)OC发出命令,将DR 中的数100装入通用寄存器

R_1,原来R_1中的数10被冲掉。

-

操作控制部分用来发出管理和指挥全机工作的

控制信号。 -

水平型微指令:一次能定义并执行多个并行操作微命令的微指令 (一次可以完成多个操作)

-

要使流水线具有良好性能,必须使流水线畅通流动,不发生断流的三种相关是

资源相关数据相关控制相关。 -

总线是数据传送的公共通路

-

总线的根数(宽度)是由总线的物理特性决定的。

-

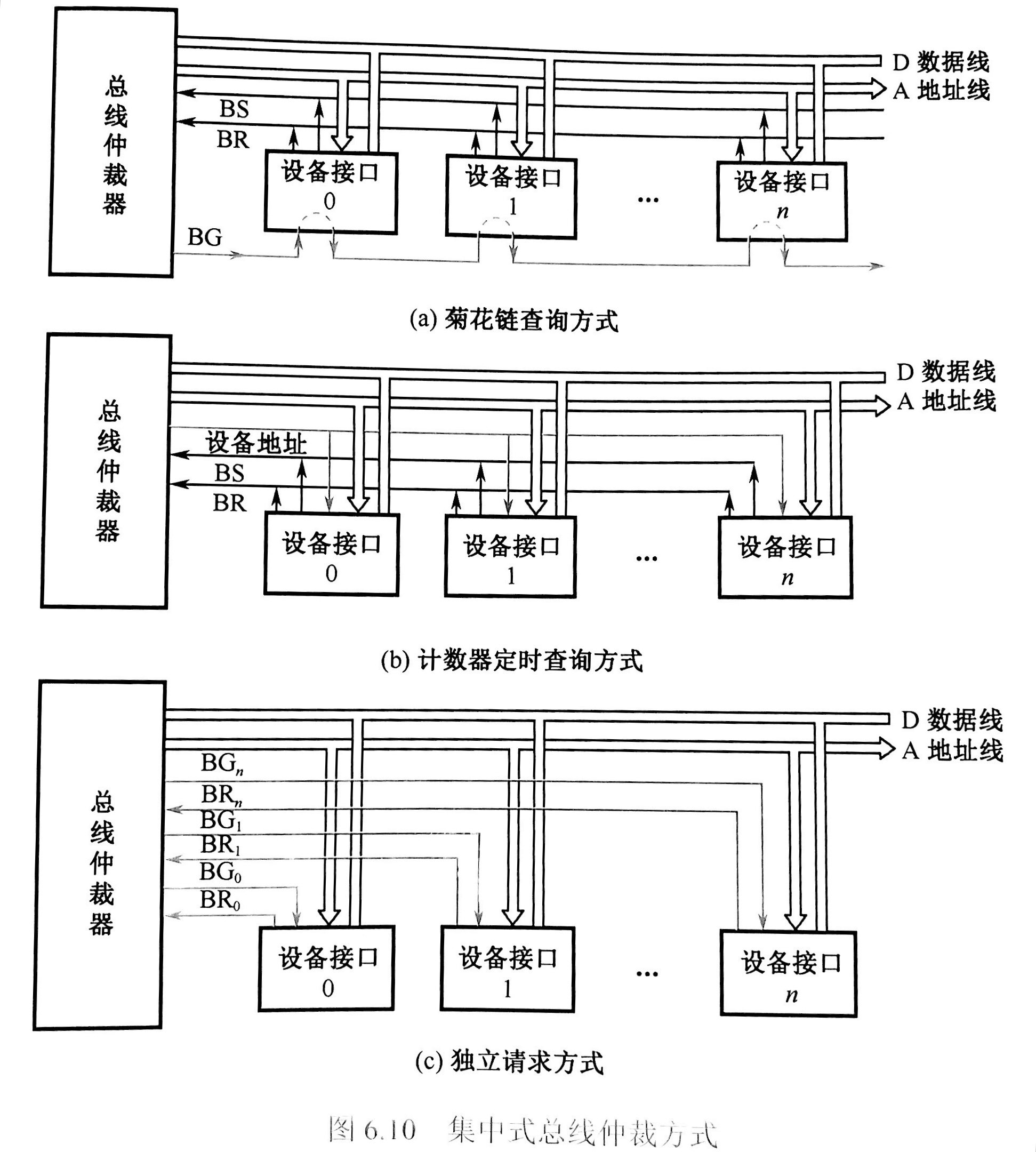

区分

-

计数器定时查询方式:总线上的任一设备要求使用总线时,通过 BR 线发出总线请求。总线仲裁器接到请求信号以后,在 BS 线为“0”的情况下让计数器开始计数,计数值通过一组地址线发向各设备。每个设备接口都有一个设备地址判别电路,当地址线上的计数值与请求总线的设备地址相一致时,该设备置“1”BS 线,获得了总线使用权,此时终止计数查询。

-

中断服务程序的入口被称为中断向量

-

CPU 接管总线是在 DMA 传输结束时

-

比较通道、DMA、中断三种基本I/O方式不同点。

- (1)CPU参与度不同,通道CPU几乎不参与数据传输,可以并行处理其他任务。DMA是CPU在数据传输开始和结束时参与,过程中不干预。中断是CPU需要频繁响应中断,参与数据传输的每次请求。

- (2)硬件需求不同,通道是需要额外的通道控制器。DMA是需要DMA控制器。中断是硬件需求相对较低,但需要中断服务程序。

- (3)数据传输方式,通道是通过通道程序控制数据传输,DMA是直接在外设与内存之间传输数据块。中断是通过中断服务程序处理每次数据传输请求。

-

-

-

-

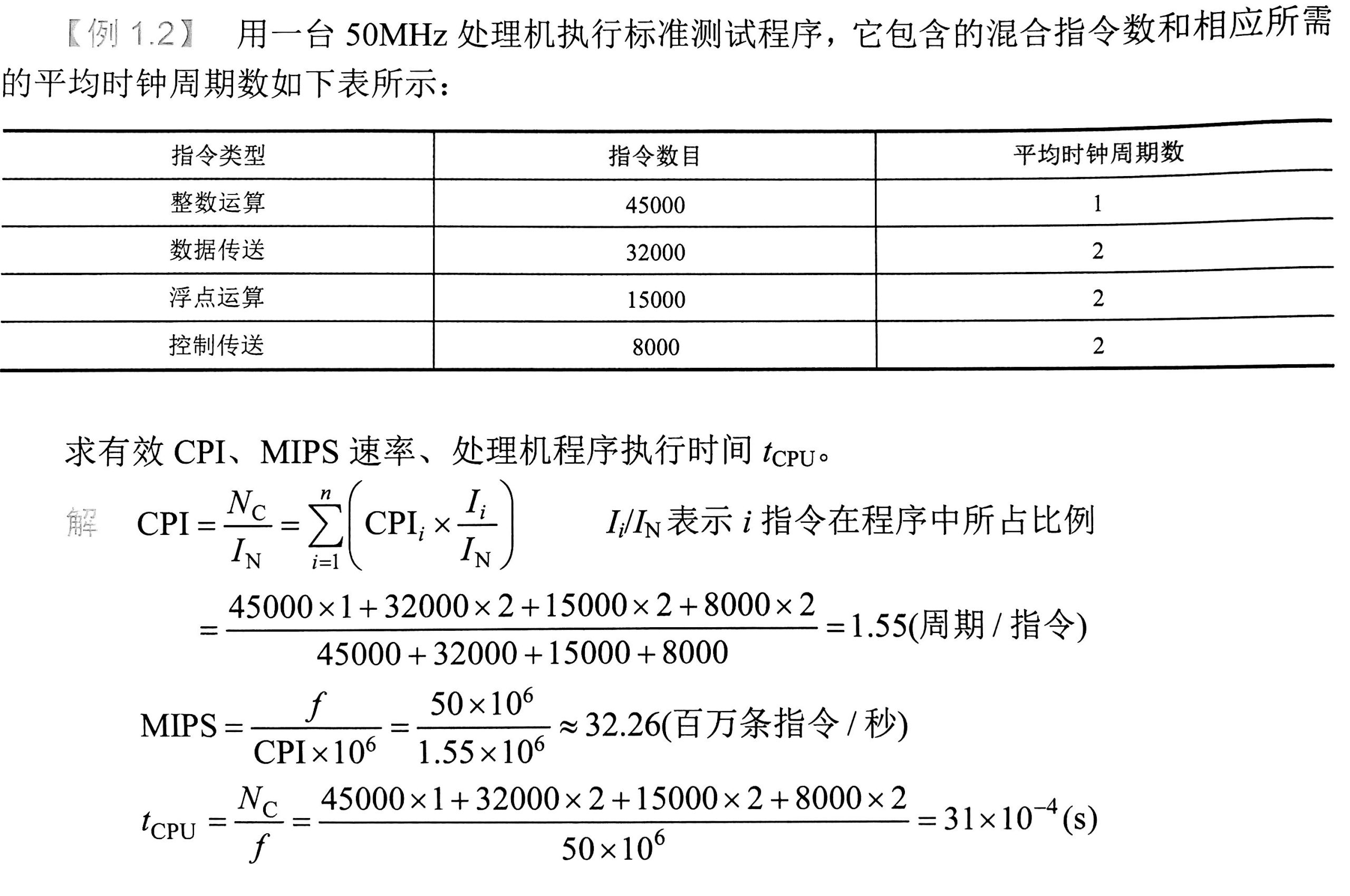

存储器容量为 32 字,每字长 64 位。存储模块数 m = 4,存储周期 T = 200ns,数据总线宽度为 64 位,总线传输周期 τ = 50ns。要求计算顺序存储器和交叉存储器在连续读取 4 个字时的带宽。

-

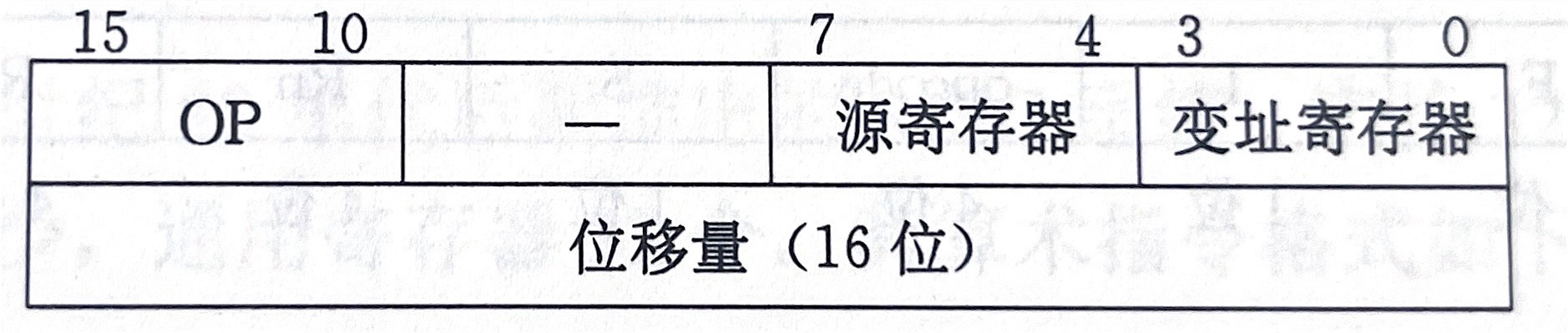

某16位机的指令格式如下所示,其中op为操作码,试分析指令格式的特点

点击查看完整内容(1)双字长二地址指令,用于访问存储器。

(2)操作码字段OP为6位,可以指定 2^6=64 种操作。

(3)一个操作数在源寄存器(共16个),另一个操作数在存储器中(由变址寄存器和位移量决定),所以是 RS型指令。 -

已知某机采用微程序控制方式,控存容量为512×48位。微程序可在整个控存中实现转移,控制库转移的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式。请问:微指令的三个字段分别应为多少位?

点击查看完整内容因为容量为512*48位,所以下址字段需用9位,控制微程序转移的条件有4个,所以判别测试字段需4位或(3位译码),因此操作控制字段的位数48-9-4=35位(或 48-9-3=36位)

本文作者为wzzyhg,转载请注明。